What is a Programmable Logic?

It is a logic element whose function is not restricted to a particular function. It may be programmed at different points of the life cycle. At the earliest, it is programmed by the semiconductor vendor (standard cell, gate array), by the designer prior to assembly, or by the user, in the circuit.

What are Programmable Logic Devices?

PLDs are ICs with a large number of gates and flip flops that can be configured with basic software to perform a specific logic function or to perform the logic for a complex circuit. Unlike a logic gate, which has a fixed function, a PLD has an undefined function at the time of manufacture. Before the PLD can be used in a circuit it must be programmed, that is, reconfigured.

Suggested Read:

When you talk about the base of any electronic device, the following 3 things play a pivotal role: memory, microprocessors, and logic.

- Memory devices store random information such as the contents of a spreadsheet or database.

- Microprocessors execute software instructions to perform a wide variety of tasks such as running a word processing program or video game.

- Logic devices provide specific functions, including device-to-device interfacing, data communication, signal processing, data display, timing and control operations, and almost every other function a system must perform.

Types of Programmable Logic:

Programmable logic devices are available in many different types. The current range of devices span from small devices capable of implementing only a handful of logic equations to huge FPGAs that can hold an entire processor core and peripherals. In addition to this incredible difference in size, there are many variations in the architecture.

Programmable logic devices can be divided into three distinct architectural groups.

- Simple Programmable Logic Devices – SPLDs

- Complex Programmable Logic Devices – CPLDs

- Field Programmable Gate Arrays – FPGAs

1. Simple Programmable Devices:

SPLDs are the simplest, smallest, and least-expensive type of programmable logic device. These devices typically have logic gates laid out in arrays where the interconnection between these arrays is configurable by the user.

The term SPLD covers several types of devices:

- Programmable Logic Array (PLA) – This device has both programmable AND and OR planes.

- Field Programmable Logic Array (FPLA) – Same as PLA but can be erased and reprogrammed.

- Programmable Array Logic (PAL) – This device has a programmable AND plane and a fixed OR plane.

- GAL – This device has the same logical properties as the PAL but can be erased and reprogrammed

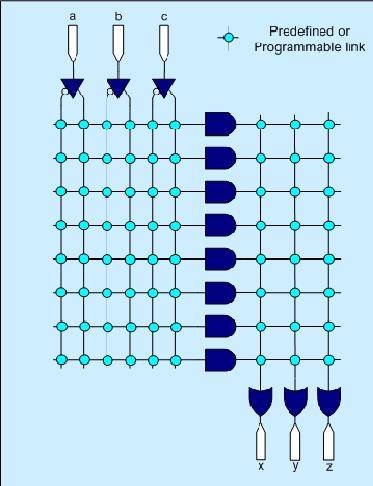

The figure shows a general structure of an SPLD. The connection link across two wires can either be predefined or programmable depending on the type of SPLD.

Programmable Logic Array:

These are the most configurable of the SPLDs. They consist of two levels of logic gates, an array of AND gates and an array of OR gates, both arrays of which are user-programmable. The structure of a PLA allows any of its inputs (and the complement of its inputs) to be AND’ed together in the AND plane which will correspond to the product term of its inputs. Also, each output of the OR plane can be configured to give the logical sum of any outputs of the AND plane. This structure allows the implementation of logic functions in the sum-of-products form. PLAs are particularly useful for large designs that require many common product terms that can be used by several outputs. This is illustrated in Fig 3 shows that the product term (a&b) is used by both the x and z outputs. The downside of the PLA device is the price of manufacture and speed. This device has two levels of programmable links and signals take a relatively long time to pass through programmable links as opposed to pre-defined ones.

Programmable Array Logic:

The speed problems associated with the PLA were addressed with the development of the PAL. The advantage of a PAL is that they are faster due to having only a single programmable array. However, this limits the number of product terms that can be OR’ed together. Because of this, several variants of the device are produced with different numbers of inputs and outputs, and different sizes of OR gate arrays. Also, many PALs support registered or latched outputs therefore if necessary the output can be stored in the flip-flop until the next clock edge and sequential designs can be realized. The structure for such a device is shown in Fig below.

2. Complex Programmable Logic Device

This group covers the middle ground in terms of complexity and density between SPLDs and FPGAs. CPLDs can handle significantly larger designs than SPLDs, but provide less logic than field programmable gate arrays (FPGAs). CPLDs contain several logic blocks, each of which includes eight to 500 macrocells. For most practical purposes, CPLDs can be thought of as multiple SPLDs (plus some programmable interconnect) in a single chip. The typical structure of a CPLD is shown in Fig 5. Each of the 16 logic array blocks shown is the equivalent of one SPLD. However, in an actual CPLD, there may be more (or less) than 16 logic array blocks. Also, each of these logic array blocks are themselves comprised of macrocells and interconnect wiring, just like an ordinary SPLD.

The larger size of a CPLD allows you to implement either more logic equations or a more complicated design. Most complex programmable logic devices contain macro cells with a sum-of-product combinatorial logic function and an optional flip-flop. Complex programmable logic devices feature predictable timing characteristics that make them ideal for critical, high-performance control applications. Typically, CPLDs have a shorter and more predictable delay than FPGAs and other programmable logic devices. Because they are inexpensive and require relatively small amounts of power, CPLDs are often used in cost-sensitive, battery-operated portable applications. CPLDs are also used in simple applications such as address decoding.

Because CPLDs can hold larger designs than SPLDs, their potential uses are more varied. They are still sometimes used for simple applications like address decoding, but more often contain high-performance control-logic or complex finite state machines. At the high end (in terms of numbers of gates), there is also a lot of overlap in potential applications with FPGAs. Traditionally, CPLDs have been chosen over FPGAs whenever high-performance logic is required. Because of its less flexible internal architecture, the delay through a CPLD (measured in nanoseconds) is more predictable and usually shorter.

3. Field Programmable Logic Arrays:

Field Programmable Gate Arrays are a two-dimensional array of logic blocks and flip-flops with electrically programmable interconnections between logic blocks.

The interconnections consist of electrically programmable switches which are why FPGA differs from Custom ICs, as Custom IC is programmed using integrated circuit fabrication technology to form metal interconnections between logic blocks.

FPGAs can be used to implement just about any hardware design. One common use is to prototype a system that will eventually find its way into an ASIC. However, especially if the product has to be available as soon as possible then there is no reason why the FPGA can’t be in the final product. Whether it does or not depends on the balance between development time and costs, and cost of the final device (number of required parts).

Figure 6 illustrates a typical FPGA architecture. There are three key parts of its structure: logic blocks, interconnect, and I/O blocks. The I/O blocks form a ring around the outer edge of the part. Each of these provides individually selectable input, output, or bi-directional access to one of the general-purpose I/O pins on the exterior of the FPGA package. Inside the ring of I/O blocks lies a rectangular array of logic blocks. And connecting logic blocks to logic blocks and I/O blocks to logic blocks is the programmable interconnect wiring.

The logic blocks within a FPGA can be as small and simple as the macro cells in a PLD (a so-called fine-grained architecture) or larger and more complex (coarse-grained). However, they are never as large as an entire PLD, as the logic blocks of a CPLD are. The logic blocks in a FPGA are generally nothing more than a couple of logic gates or a look-up table and a flip-flop.

Because of all the extra flip-flops, the architecture of a FPGA is much more flexible than that of a CPLD. This makes FPGAs better in register-heavy and pipelined applications. They are also often used in place of a processor-plus-software solution, particularly where the processing of input data streams must be performed at a very fast pace. In addition, FPGAs are usually denser (more gates in a given area) and cost less than their CPLD cousins, so they are the de facto choice for larger logic designs.

Advantages of Programmable Logic Devices:

Programmable logic devices offer a number of important advantages over fixed logic devices, including:

- Design Flexibility: PLDs offer customers much more flexibility during the design cycle because design iterations are simply a matter of changing the programming file, and the results of design changes can be seen immediately in working parts.

- Improved Reliability: Lower power plus fewer interconnections and packages translate into greatly improved system reliability.

- Lower Power: CMOS and fewer packages combine to reduce power consumption.

- Reduced complexity: Since PLDs consume lower power requirements less board space and simpler testing procedures.

- PLDs are field-programmable i. e. can be programmed outside of the manufacturing environment

- PLDs are erasable and reprogrammable i.e allows updating a device or correction of errors and allows to reuse the device for a different design – the ultimate in reusability!

Applications of Programmable Logic Devices:

- Glue Logic: Glue logic is the Simple logic circuits used to connect together more complex circuits which are not perfectly compatible. For example, an ASIC chip may contain large functions, such as a microprocessor, memory block or communications block, which are tied together via small amounts of glue logic. At the printed circuit board (PCB) level, glue logic may be implemented with simple “jelly bean” chips (“glue chips”) that contain a few gates all the way to programmable logic devices.

One challenge is how to connect the FXS chipset to the Atheros SoC (glue logic in the figure above). This glue logic was straight forward for the IP04 as the Blackfin CPU has a rich set of interfaces with good DMA support. The Atheros SoC is not quite as feature-rich. It does have an SPI bus for talking to the SPI flash. This only has one chip select line. Another example of glue logic is the address decoder which with older processors like the 6502 or Z80 had to be added externally to divide up the addressing space of the processor into RAM, ROM, and I/O. Newer versions of the same processors (such as the WDC565816 or Zilog eZ80) instead have internal address decoders so glueless interfacing to the most common external devices becomes possible.

- State Machines: A state machine is a sequential logic function that controls other logic functions by sequencing control signals in response to input signals. The most common implementation of a state machine is a digital logic function in which the outputs are a function of both the present inputs and the previous state. The previous state is usually stored in a state register.

For example, a state machine may wait in a particular state until a certain signal is asserted and then move to a new state. The machine travels from state to state in response to the input signals. Implementing control functions as state machines is a common application for PLDs (programmable logic devices). For an example, there are three main components to implementing PLIO [Programmable Low-Latency Input Output]: the software driver, the programmable state machine, and the flexible IO.In order for PLIO to address the highest number of bus protocols, part of the bus interface is controlled in software while the low-latency portions of the protocol are programmed into the state machine. The software driver handles the high latency parts of the bus protocol and the supplying and receiving of data and addresses to the interface, while the programmable state machine manages the control signals and interface timing. The flexible IO of PLIO allows for pin compatibility across the control, address and data signals.

- Counters: An instrument which, in its simplest form, provides an output that corresponds to the number of pulses applied to its input.Most digital counters operate in the binary number system since binary is easily implemented with electronic circuitry. Binary allows any integer (whole number) to be represented as a series of binary digits, or bits, where each bit is either a 0 or 1 (off or on, low or high, and so forth).

For an example, a digital watch contains numerous counters in its large-scale integration (LSI) chip, usually implemented with complementary metal oxide semiconductor (CMOS) technology. For another example, digital computers may contain counters in the form of programmable interval timers that count an integral number of clock pulses of the known period, and then generate an output at the end of the count to signal that the time period has expired.

Other Uses:

- Synchronization

- Decoders

- Bus Interfaces

- Parallel-to-Serial

- Serial-to-Parallel

Conclusion

Over the last few years, programmable logic suppliers have made such phenomenal technical advances that PLDs are now seen as the logical solution of choice from many designers. One reason for this is that PLD suppliers such as Xilinx are “fabless” companies; instead of owning chip manufacturing foundries, Xilinx out sources that job to partners like IBM Microelectronics and UMC, whose chief occupation is making chips. This strategy allows Xilinx to focus on designing new product architectures, software tools, and intellectual property cores while having access to the most advanced semiconductor process technologies. Advanced process technologies help PLDs in a number of key areas: faster performance, integration of more features, reduced power consumption, and lower cost. Today Xilinx is producing programmable logic devices on a state-of-the-art 0.13-micron low-k copper process – one of the best in the industry.

Just a few years ago, for example, the largest FPGA was measured in tens of thousands of system gates and operated at 40 MHz. Older FPGAs also were relatively expensive, costing often more than $150 for the most advanced parts at the time. Today, however, FPGAs with advanced features offer millions of gates of logic capacity, operate at 300 MHz, can cost less than $10, and offer a new level of integrated functions such as processors and memory.

Just as significant, PLDs now have a growing library of intellectual property (IP) or cores – these are predefined and tested software modules that customers can use to create system functions instantly inside the PLD. Cores include everything from complex digital signal processing algorithms and memory controllers to bus interfaces and full-blown software-based microprocessors. Such cores save customers a lot of time and expense. It would take customers months to create these functions, further delaying a product introduction.

The value of programmable logic has always been its ability to shorten development cycles for electronic equipment manufacturers and help them get their products to market faster. As PLD suppliers continue to integrate more functions inside their devices, reduce costs, and increase the availability of time-saving IP cores, programmable logic is certain to expand its popularity with digital designers. Logic devices provide specific functions, including device-to-device interfacing, data communication, signal processing, data display, timing and control operations, and almost every other function a system must perform.

thankx alotssss this is very helpful for me

You are welcome Naina!

how to download programmabe logic devices ppt

Hi Surekha,

You have an option to mail this post.

If you are looking for presentation format, we do not prepare it.

Comments are closed.